## PD IEC/TR 63018:2015

## **BSI Standards Publication**

Flexible printed circuit boards (FPCBs) — Method to decrease signal loss by using noise suppression materials

#### **National foreword**

This Published Document is the UK implementation of IEC/TR 63018:2015.

The UK participation in its preparation was entrusted to Technical Committee EPL/501, Electronic Assembly Technology.

A list of organizations represented on this committee can be obtained on request to its secretary.

This publication does not purport to include all the necessary provisions of a contract. Users are responsible for its correct application.

© The British Standards Institution 2016. Published by BSI Standards Limited 2016

ISBN 978 0 580 91193 4 ICS 31.180

## Compliance with a British Standard cannot confer immunity from legal obligations.

This Published Document was published under the authority of the Standards Policy and Strategy Committee on 31 January 2016.

#### Amendments/corrigenda issued since publication

Date Text affected

## **IEC TR 63018**

Edition 1.0 2015-12

# TECHNICAL REPORT

Flexible printed circuit boards (FPCBs) – Method to decrease signal loss by using noise suppression materials

INTERNATIONAL ELECTROTECHNICAL COMMISSION

ISBN 978-2-8322-3082-4

Warning! Make sure that you obtained this publication from an authorized distributor.

### CONTENTS

| FOREWORD                                                 |                                                                          | 3  |

|----------------------------------------------------------|--------------------------------------------------------------------------|----|

| INTRODUCT                                                | ION                                                                      | 5  |

| 1 Scope                                                  |                                                                          | 6  |

| 2 Normati                                                | ve references                                                            | 6  |

| 3 Test gui                                               | deline                                                                   | 6  |

| 3.1 Ap                                                   | paratus                                                                  | 6  |

| 3.1.1                                                    | Network analyzer                                                         |    |

| 3.1.2                                                    | Block diagram for signal loss measuring                                  | 6  |

| 3.2 Te                                                   | st specimen                                                              | 7  |

| 3.2.1                                                    | Structure                                                                | 7  |

| 3.2.2                                                    | Preparation                                                              | 8  |

| 3.2.3                                                    | Test method                                                              | 8  |

| 3.2.4                                                    | Calculation                                                              | 9  |

| 3.2.5                                                    | Test result                                                              | 9  |

| 3.2.6                                                    | Analysis                                                                 |    |

|                                                          | provement method of signal loss for a shield FPCB                        |    |

| Annex A (no                                              | mative) Block diagram of signal loss test system                         | 14 |

| Figure 4 D                                               | are labiald EDCD                                                         | _  |

| _                                                        | are/shield FPCB                                                          |    |

| _                                                        | crement of signal loss using NSMs                                        |    |

| •                                                        | gnal loss test system                                                    |    |

|                                                          | chematic diagram for two type of test specimen                           |    |

| Figure 5 – C                                             | oss-section of shield FPCB                                               | 8  |

| Figure 6 – D                                             | fference of signal loss between bare and shield FPCBs                    | 9  |

| Figure 7 – Signal loss value of the bare and shield FPCB |                                                                          |    |

| Figure 8 – Si                                            | gnal loss variation according to the Cu conductive layer thickness       | 11 |

| _                                                        | gnal loss variation according to the Cu signal line width                |    |

| •                                                        | wo types of structure for FPCB                                           |    |

|                                                          | Electric field diagram for two types of shield FPCB                      |    |

| _                                                        | Block diagram of signal loss test system                                 |    |

| _                                                        |                                                                          |    |

| rigure A.2 –                                             | Signal loss test system according to the Agilent network analyzer N5230A | 14 |

| Table 1 – Co                                             | mparison of cut-off frequency with bare/shild FPCB                       | 10 |

#### INTERNATIONAL ELECTROTECHNICAL COMMISSION

# FLEXIBLE PRINTED CIRCUIT BOARDS (FPCBs) – METHOD TO DECREASE SIGNAL LOSS BY USING NOISE SUPPRESSION MATERIALS

#### **FOREWORD**

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international

consensus of opinion on the relevant subjects since each technical committee has representation from all

interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

- 5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any services carried out by independent certification bodies.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

The main task of IEC technical committees is to prepare International Standards. However, a technical committee may propose the publication of a technical report when it has collected data of a different kind from that which is normally published as an International Standard, for example "state of the art".

IEC TR 63018, which is a technical report, has been prepared by IEC technical committee 91: Electronics assembly technology.

The text of this technical report is based on the following documents:

| Enquiry draft | Report on voting |

|---------------|------------------|

| 91/1284/DTR   | 91/1309/RVC      |

Full information on the voting for the approval of this technical report can be found in the report on voting indicated in the above table.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

The committee has decided that the contents of this publication will remain unchanged until the stability date indicated on the IEC website under "http://webstore.iec.ch" in the data related to the specific publication. At this date, the publication will be

- · reconfirmed,

- · withdrawn,

- replaced by a revised edition, or

- amended.

A bilingual version of this publication may be issued at a later date.

IMPORTANT – The 'colour inside' logo on the cover page of this publication indicates that it contains colours which are considered to be useful for the correct understanding of its contents. Users should therefore print this document using a colour printer.

#### INTRODUCTION

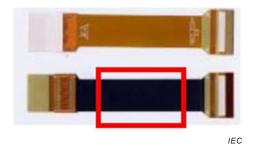

In recent years, since the use of smart phones, and other mobile and display devices has increased significantly, the supply of FPCBs has also been largely extended. Specifically, since the FPCB devices seek high speed performance, the requirements with respect to electromagnetic interference (EMI) suppression in the devices has also grown in importance. Therefore, FPCBs used inside smart phones employ noise suppression materials (NSMs) to solve EMI problems, as shown in Figure 1.

Figure 1 - Bare/shield FPCB

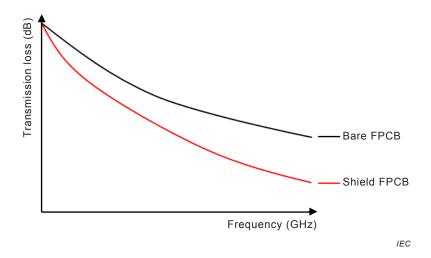

However, an application of noise suppression materials (NSMs) for FPCBs reaches the limit concerning the problem of incrementation of signal loss. Therefore, FPCB and NSMs manufacturers need to analyse signal loss variations of FPCBs shielded by NSMs, as shown in Figure 2.

Figure 2 – Increment of signal loss using NSMs

As FPCBs are used with high frequency, the problem of signal loss becomes more significant. As the user of FPCBs has a demand for the lowest value of signal loss by using NSMs, suppliers of FPCBs have to anticipate an appropriate design in order to achieve an adequate signal loss value.

## FLEXIBLE PRINTED CIRCUIT BOARDS (FPCBs) – METHOD TO DECREASE SIGNAL LOSS BY USING NOISE SUPPRESSION MATERIALS

#### 1 Scope

This Technical Report specifies a guideline for improvement of signal loss by using noise suppression materials (hereafter referred to as NSMs) for FPCBs.

This Technical Report also indicates a measuring method of signal loss variations of FPCBs using NSMs using network analyzer equipment. In addition, this method only measures the value of the signal loss variation by using NSMs for FPCBs. This report, however, neither determines nor indicates the structure or material of FPCBs.

#### 2 Normative references

The following documents, in whole or in part, are normatively referenced in this document and are indispensable for its application. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

IEC 62333-1:2006, Noise suppression sheet for digital devices and equipment – Part 1: Definitions and general properties

#### 3 Test guideline

#### 3.1 Apparatus

#### 3.1.1 Network analyzer

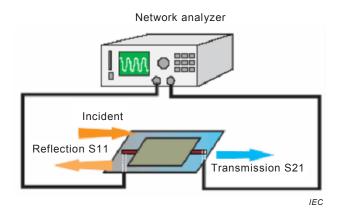

A network analyzer is utilized to identify signal loss data at a specific frequency range of FPCBs.

#### 3.1.2 Block diagram for signal loss measuring

Figure 3 indicates one of the examples of the network analyzer setup.

Figure 3 – Signal loss test system